贝博体育艾弗森代言:经典款嵌入式智能小车的设计技巧提供硬件选型

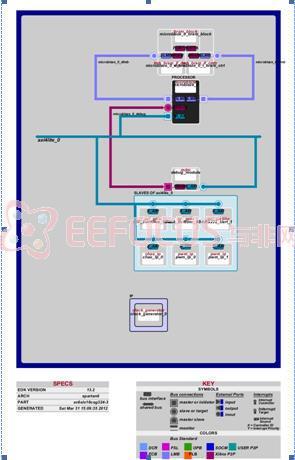

,特别是嵌入式系统,一般都是基于单片机或者ARM的嵌入式系统,大多数都由软件系统和硬件系统组成的,硬件系统方面,跟传统的搭建硬件环境一样,只能做相对裁剪和功能拓展,但是,本项目的课题是通过xilinx的开发板搭建嵌入式的硬件环境,从最小系统到IP核的添加,都是根据自身的需求进行拓展的,实现一对一的拓展,不浪费资源,而且基于的嵌入式系统的最大有优点是,既有PFGA的并行执行效率,又有嵌入式软件的逻辑过程分析控制。

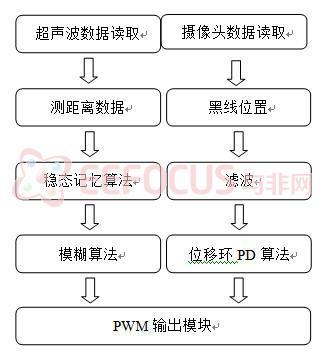

使用Spartan-6的XC6SLX16 CSQ234 作为主控制器,传感器使用摄像头ov6620图像采集模块(兼测路径),使用超声波模块(HCSR04)测距,由于两者具有互补特性,所以能很好的控制小车的运作时的状态,采用模糊算法计算出电机所需要的转速,和舵机的转角,以此来实现稳步渐进。

解决方案:采用可编程逻辑器件FPGA作为控制器。FPGA能轻松实现复杂的逻辑功能,规模大,密度高,体积小,稳定性高,IO资源丰富,易于外围功能扩展,随着FPGA的成本逐步降低,而且基于FPGA的嵌入式系统的搭建也成为可行,既有传统嵌入式的软件灵活性,也有FPGA的并行快速执行效率。

解决方案:由于直流电机的功耗大,决定采用7.2V,2000mAh的电池为供电源,采用LM25xx系列单片集成开关电源作为降压芯片,能够给大家提供大功率的输出,转换效率高,性能稳定。

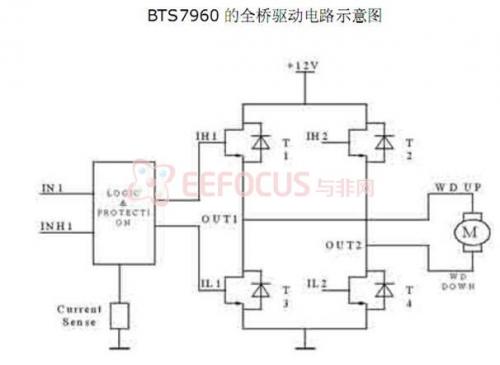

解决方案:采用BTS7960B搭建全桥驱动,能够完全满足大功率的输出,分别驱动两个电机。

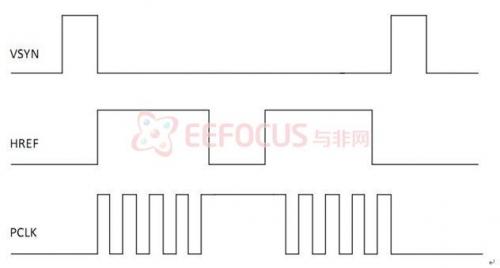

OV6620的同步信号时序如下:场同步信号VSYN 为两个正脉冲之间扫描一帧的定时,即

完整的一帧图像在两个正脉冲之间;行同步信号href 扫描该帧图像中各行像素的定时,

即高电平时为扫描一行像素的有效时间;像素同步信号 PCLK为读取有效像素值提供同步信

号,高电平时输出有效图像数据。下图为OV6620 VSYN、href、PCLK三个同步信号之

VYNSC是判断是否一幅图像开始,周期是 20ms, 其中高电平维持的时间很短;href 是判

断是否一行图像的开始,周期是 63us 左右,其中高电平维持的时间为 40US,低电平持续

当然实际上没这么多,消隐和无效信号去掉之后只有 292行;有效的灰度数据是在行中

断之后的上升沿内,所以不要在行中断后的 23US 后采集。计算一下一行 OV6620 有多

少个点: 40us/110ns=363, 消隐和无效信号去掉之后只有 356 个点。足以证明

机的总线,根本没办法捕捉到这个信号,此时PCLK 的波形已经变为尖波,绝对没意义捕捉

系统中采用了BTS7960B搭建全桥驱动,能够完全满足大功率的输出,分别驱动两个电机。

BTS7960B 的芯片内部为一个半桥。INH引脚为高电平,使能BTS7960。IN引脚用于确定哪个MOSFET 导通。IN=1 且INH=1 时,高边MOSFET 导通,OUT 引脚输出高电平;IN=0 且INH=1 时,低边MOSFET 导通,OUT 引脚输出低电平。SR 引脚外接电阻的大小,能调节MOS管导通和关断的时间,具有防电磁干扰的功能。

3.5下图是由FPGA构建的最小嵌入式系统,是根据xilinx官方的EDK要求搭建的。

软件设计大致上可以分为三部分,第一部分是最小系统的搭建(软件初始化),第二部分是外部硬件的驱动,第三部分是核心算法。

外部硬件驱动,选择以IP核的形式添加到最小系统历来,用硬件描述语言编写驱动核心代码,然后软件通过寄存器驱动外部硬件。

在EDK设计中,可以新建测试代码,自动生成测试代码,通过串口打印验证结果。

在增加IP核过程中,应该要依据超声波的时序要求,用硬件描述语言描述驱动的过程。

由于需要两路的PWM来分别操作舵机和直流电机,所有PWM的调试时至关重要的。